# 第1章 绪 论

现代社会逐步增加了对舒适、交通和医疗方面的电气的依靠,促使发电、电力传输和电力管理技术的巨大进步。这些进步应归功于控制电的流动的功率器件性能的增强。在 20 世纪 50 年代固体器件替代真空管后,业界依靠硅双极器件,例如双极结型功率晶体管和晶闸管。尽管这些器件快速增长以服务于更广泛的系统需求,在复杂控制方面的基本限制和保护电路导致大的体积和昂贵的解决措施。在 20 世纪 70 年代,数字电子学的 MOS 技术出现使创造出用于功率开关电气的新一类器件成为可能。这些硅功率 MOSFET 已经广泛地用于工作电压较低(低于 100 V)的高频电气中。在 20 世纪 80 年代,MOS 和双极合并的物理机理使创造出另一类器件成为可能。在这些器件中最成功的创新是绝缘栅双极型晶体管(IGBT)。或许除高压直流(DC)传输系统外,IGBT 的大功率密度、简单接口和坚固性已经使它成为所有中功率和大功率电气的首选。由于MOS 栅结构介人可能威胁到常规功率晶闸管最终剩下的堡垒。

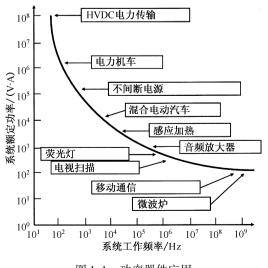

系统要求功率器件工作在很宽的功率和频率范围内。功率器件的应用与工作频率的关系,如图 1.1 所示。像高压直流(HVDC)电力传输和机车驱动,大功率系统要求在较低的频率控制 兆瓦级的功率工作。随着工作频率的提高,对器件的额定功率减小,典型的微波炉用器件处理大约100 W。所有这些电气都采用硅器件。晶闸管适合于低频、大功率电气,IGBT 适合于中频和中 功率电气,功率 MOSFET 适合于高频电气。

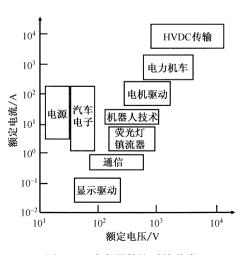

功率器件应用划分的另一种方法是根据它们要求处理的电流和电压,如图 1.2 所示。在图的大功率端,可用的能单独处理大于 6000 V 和 2000 A 的晶闸管,用单个芯片可控制超过 10 MW 的功率。这些器件适用于 HVDC 功率传输和机车驱动(牵引)。对于要求工作电压在 300 V ~ 3000 V 之间具有可观的电流处理能力的系统,IGBT 是优选方案。当要求电流小于 1 A 时,适合集成多个器件在一个芯片上,以便为系统提供更强的功能,例如在通信和显示驱动方面。然而,当电流超过几安培,如用于汽车电子系统和开关电源模块,使用具有合适的集成电路控制的分立功率MOSFET 器件具有更好的性价比。结论是现在没有哪一种器件结构适合于所有的应用,为进一步创新留下了广阔的空间。

图 1.1 功率器件应用

图 1.2 功率器件按系统分类

#### 1.1 理想和典型的功率开关模型

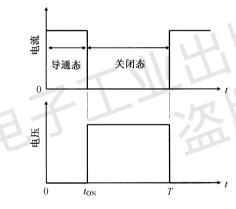

理想的功率器件必须具有在零功率消耗下控制功率流向负载的能力。在系统中遇到的负载可能是电感性的(如电机和螺线管)、电阻性的(如加热器和灯丝)或电容性的(如变换器和 LCD 显示器)。最常见的是用控制电路可调节产生脉冲电流,将它加在基极上周期性地控制功率器件的导通,使功率传输到负载。图 1.3 所示是通过功率开关传输功率的理想波形。在每个开关周期内,开关在到  $t_{\rm on}$ 时间内保持导通,在 T 期间保持关断。对于理想的开关,在导通状态电压降是零,结果是没有功率消耗。类似地,在关断状态,理想功率开关的漏电流是零,结果是没有功率消耗。此外,假设功率开关能使在导通和关断之间瞬间转换,也没有功率损失。

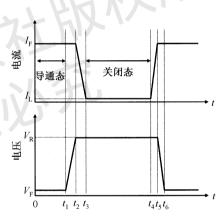

用观察典型的功率开关在导通、关断以及开关瞬间的波形展示功率消耗。如图 1.4 所示, 典型的功率器件在导通态展示了一个电压降( $V_e$ ), 它导致了在导通态的功率消耗, 由下式给出

$$P_{\rm L}(导通态) = \delta I_{\rm F} V_{\rm F} \tag{1.1}$$

这里  $I_{\rm E}$  是导通电流。在该表达式中, $\delta$  是由下式给出的占空比

$$\delta = t_1 / T \tag{1.2}$$

这里T是时间周期(工作频率的倒数)。

图 1.3 功率输运的理想波形

图 1.4 功率输运的典型波形

在关断态也有功率消耗,由下式给出

$$P_{\rm L}(美断态) = (1-\delta)I_{\rm L}V_{\rm R} \tag{1.3}$$

由于施加反向偏置电压 ( $V_{\rm R}$ ), 这里  $I_{\rm L}$  是在器件关断态的漏电流。如果开关时间小到可以和周期相比,该表达式是正确的。如果该假设无效,功耗可由下式得到

$$P_{L}(\xi) = (t_4 - t_3) I_{L} V_{R} / T$$

(1.4)

最常见的是,和其他元件比较关断态的功耗是小得可以忽略不计。然而,在温度升高和对肖特基接触施加反向电压时这就不再正确了。

开关期间发生的功耗在关断瞬间和导通瞬间必须分别对待。关闭瞬间,典型的负载是感性的,通过开关的电压迅速上升到直流电源电压,伴随着流过开关的电流减小。对于图 1.4 所示的线性波形,关闭瞬间的功耗可由下式计算

$$P_{\rm L}$$

(关闭瞬间) =  $0.5(t_3 - t_1)I_{\rm F}V_{\rm R}f$  (1.5)

这里 ƒ 是工作频率。类似方法, 在导通瞬间的功耗可由下式计算

$$P_{L}$$

(导通瞬间)=0.5 $(t_{6}-t_{4})I_{F}V_{R}f$  (1.6)

在开关产生的总功耗是将这些项结合在一起获得

$$P_{L}($$

总功耗 $) = P_{L}($ 导通态 $) + P_{L}($ 关断态 $) + P_{L}($ 关断瞬间 $) + P_{L}($ 导通瞬间 $)$  (1.7)

在低工作频率下,导通态功耗通常是主要的,期望开发具有低导通压降的功率开关。在高工作频率下,开关功耗通常是主要的,期望开发具有快开关速度或小的瞬变时间的功率开关。遗憾的是,在大多数设计中,通常必须在最小导通态和开关功耗之间折中。随着功率开关技术的进步,优化后设计的总功耗不断减小,增强了电力系统的效率。

## 1.2 理想和典型的功率器件参数

如上所述, 硅功率器件服务业界超过了50年, 但是不能认为有理想的器件特性。一般地, 电力电子电路要求整流管控制电流的方向和功率开关调整电流的持续时间。这些元件还没有展示出理想的特性, 功率电路要求的理想特性是防止功率消耗。

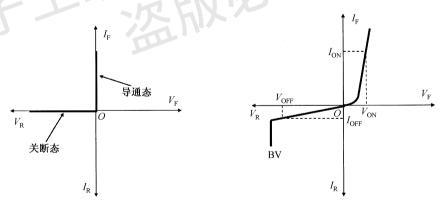

理想的功率整流管应展示出图 1.5 所示的电流-电压(*i-v*)特性。在正向导通模式,工作在图中的第一象限,应能在零导通压降下通过任何量的电流。在反向阻断模式,工作在图中的第三象限,应能在零漏电流下,保持任何值的电压。进一步,理想的整流管应能以零开关时间在导通态和关断态之间开关。

实际的硅功率整流器展示的 i-v 特性如图 1.6 所示。当在导通态流过电流时,它们有有限的电压降( $V_{\rm ON}$ ),导致导通时的功耗。当在关断阻断电压时,它们有有限的漏电流( $I_{\rm OFF}$ ),产生关断态功耗。此外,针对击穿电压(BV)的设计目标,必须精心选择硅器件漂移区的掺杂浓度和厚度。进一步,随着额定电压的提高,因为导通电压降增大,功率器件的功耗增加。

图 1.5 理想的功率整流管的特性

图 1.6 典型的功率整流管的特性

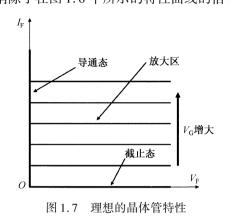

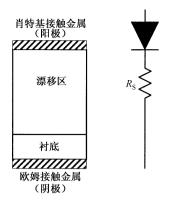

理想功率开关的 i-v 特性如图 1.7 所示。正如在理想整流管的情况一样,理想晶体管在零压降下传导电流,在零漏电流关断态下阻断电压。此外,理想器件能工作在大电流和高电压的放大区,由施加的栅偏压控制该模式下的正向饱和电流。对于理想晶体管,在放大区特性曲线间的间隔是均匀的,这表示增益是与正向电流和电压无关的。

典型的功率开关的 *i-v* 特性如图 1.8 所示。该器件展示了在导通态的电流有限的电阻,以及工作在关断态的有限的漏电流(因为该值比导通时的电流低得多,所以在图中没有显示)。典型晶体管的击穿电压也是有限的,在图中用 BV 表示。典型的晶体管在放大区能工作在大电压和大电流下。该电流受基极电流控制,而对于 MOSFET 或 IGBT 由栅电压决定(如图 1.8 所示)。用栅

压控制特性更好,因为可集成驱动电流以降低它的功耗。对于工作在沟道夹断的饱和电流模式,典型的晶体管放大区特性曲线之间的间隔是不均匀的,服从平方率。最近,有人提出一种工作在新的超线性模式的器件,并展示将其在无线基站应用中[1]。随着栅压提高,这些器件展示了在饱和漏电流特性曲线是等间隔的。当晶体管用于音频、视频或手机信号时,这是一种理想的现象,因为它消除了在图 1.8 中所示的特性曲线的信号畸变。

## 1.3 单极功率器件

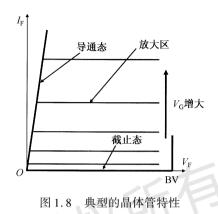

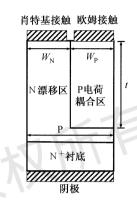

双极功率器件工作在导通态时,具有少数载流子注入。当将器件从导通态转向关断态时,必须将这些载流子去除。经由栅驱动电流或经电子 - 空穴复合过程完成电荷去除。这些过程引入可观的功耗,使功率管理效率降低。因此,在功率器件中利用单极电流导电更受欢迎。常用的单极功率二极管结构是肖特基整流管,它利用金属一半导体势全进行电流的整流。高压肖特基整流结构还包含漂移区,如图 1.9 所示,其目的是支撑反向阻断电压。随着提高阻断电压,漂移区的电阻迅速增大,这将在本章后部讨论。商用硅肖特基整流管的阻断电压可达 100 V。大于该值后,硅肖特基整流管的导通压降变得太大以至于无法实用。对于更高 BV 要求,硅 P-i-N 整流管更受欢迎,由于尽管其降低了开关特性,但是它们具有更低的导通压降。碳化硅肖特基整流管具有非常低的漂移区电阻,可以设计具有低的导通压降和优异开关特性的非常高电压的器件。

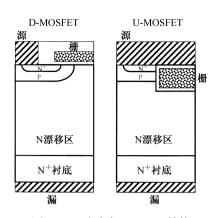

最常用的单极功率器件是硅功率金属-氧化物-半导体场效应晶体管(MOSFET)。虽然,已经探讨了如结型场效应晶体管(JFET)或静电感应晶体管(SIT)之类的结构,因为它们属常通态器件,在电力电子应用中还不普遍<sup>[2]</sup>。商用的硅功率 MOSFET 是依据图 1.10 所示的结构。在 20 世纪 70 年代,具有"平面栅"结构的 D-MOSFET 第一次被引入商用。通过使用硼和磷离子注入,接着进行热推进过程,P型基区和 N<sup>+</sup>源区与多晶硅栅电极的边缘是自对准的。N型沟道栅电极下的结由横向延伸的差所决定。器件穿过 P型基区/N 漂移区的结将正电压施加在漏端。阻断电压能力由 N 漂移区的掺杂浓度和厚度所决定。尽管低电压(小于 100 V)硅功率 MOSFET 有低的导通电阻,但是,随着阻断电压提高,漂移区电阻迅速增加,将硅功率 MOSFET 性能限制在 200 V以下。它和用于更高电压的 IGBT 的共同点是因为更小的导通态功耗。

在 20 世纪 90 年代,硅 U-MOSFET 结构可以商用了。它具有刻蚀到硅表面内的槽栅结构。 N 型沟道形成在 P 衬底区表面沟槽的侧面。沟道长度由 P 基区和 N<sup>+</sup>源区垂直延伸的差所决定,它可由掺杂离子注入能量和推进时间控制。开发硅 U-MOSFET 结构,可以消除 D-MOSFET 结构内的 JFET 结构,来减小导通电阻。

图 1.9 功率肖特基整流管结构及其等效电路

图 1.10 硅功率 MOSFET 结构

#### 1.4 双极功率器件

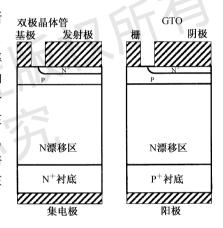

常用的硅功率双极器件是双极型晶体管和门极可关断晶闸管(GTO)。最初开发这些器件是在 20 世纪 50 年代,广泛用于功率开关电器直到 20 世纪 70 年代,当硅功率 MOSFET 和 IGBT 可用时补充了它们。双极型晶体管和GTO 的结构如图 1.11 所示。在这两种器件中,少数载流子注入漂移区调制其导电性能,降低了导通压降。然而,在开关期间,这些电荷随后必须去除,导致大的关断功耗。这些器件要求大的控制(基极或栅)电流,必须用分立器件实现,导致昂贵笨重的系统设计。为了克服这一弱点,在20 世纪 80 年代提出和发展了 MOS 双极结构。

图 1.11 硅双极器件结构

## 1.5 MOS 双极功率器件

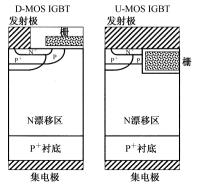

在功率开关电器中,应用最广泛的硅高压(大于300 V)器件是 IGBT,它在20世纪80年代通过结合双极型晶体管和MOSFET的工作机理开发出来<sup>[3]</sup>。IGBT的结构非常类似图1.12所示的功率

图 1.12 IGBT 器件结构

MOSFET, 仅仅是用 P<sup>+</sup>衬底换成 N<sup>+</sup>衬底。然而,这个替换产生了一个 4 层的寄生晶闸管,最初是考虑优异的性能被中断,因为它的闩锁导致栅失控的破坏性失效。幸运的是,可通过在单元内增加 P<sup>+</sup>区以抑制寄生的晶闸管,同时保持 P<sup>+</sup>衬底少数载流子注入 N 漂移区的优点,结果显著地减少它的电阻。这使得开发具有大电流的高压 IGBT 产品成为可能。

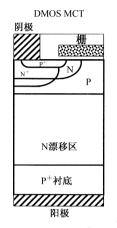

为提高电压阻断能力,必须加宽 N 漂移区,IGBT 的导通压降随之而增加。在保持小的控制电流优势的同时,为了改善导通压降,已经开发了多种 MOS 栅控晶闸管结构。第一种值得关注的结构是 MOS 控制晶闸管(MCT)<sup>[4,5]</sup>,它具有一个N型漂移区,如图 1.13 所示。和 IGBT 比较,通过允许 4 层

晶闸管结构到闩锁, 获得降低的导通压降。通过施加负栅压以形成一个电流通路, 该通路分流

N<sup>+</sup>发射极/P 基极结电流,以便上方的 NPN 晶体管的增益减到足够小,防止激活晶闸管。由此将晶闸管关断,在图 1.13 中所示的结构的一个缺点是在 P 基区内形成 P 沟 MOSFET 的复杂性。隐藏在应用中的另一个问题是缺乏电流饱和能力。如果没有栅控制电流饱和,就必须将器件和缓冲器结合在一起,这将增加系统的成本、复杂性和功耗。

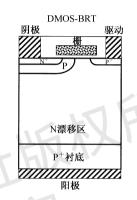

上述问题的一个解决方案是基极电阻控制晶闸管(BRT)结构<sup>[6]</sup>,如图 1.14 所示。在该结构中,将一个分流器集成到邻近的 4 层晶闸管。通过将其维持电流提高到工作电流以上,给栅上施加一个正偏压允许晶闸管导通,而施加一个负偏压将晶闸管关断。制造这种结构的工艺制造IGBT所用工艺可兼容,而其导通压降类似于 MCT 结构的。

图 1.13 MOS 控制晶闸管(MCT)结构

图 1.14 基极电阻控制晶闸管(BRT)结构

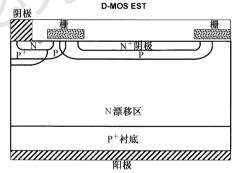

MCT 和 BRT 结构不允许在栅控制下饱和电流流过,IGBT 的主要特征是扩展了在电力电子学中的应用。该能力已经被成功结合进发射极开关晶闸管(EST)结构<sup>[7]</sup>,如图 1.15 所示。EST 结构包含 4 层晶闸管,没有直接接触到 N<sup>+</sup> 阴极区。流进 N<sup>+</sup> 阴极区的电流制约经由N 沟道 MOSFET 到阴极接触孔的电流。这提供了完全栅控电流饱和能力。然而,在 MOSFET 沟道中增加了压降,导通压降仅比 MCT 和 BRT 略大一点。

## 1.6 单极功率器件的理想漂移区

图 1.15 发射极开关晶闸管(EST)结构

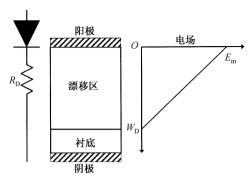

上述讨论的单极功率器件包含一个漂移区,它是用于支撑阻断电压。理想漂移区的特性(掺杂浓度和厚度)可假设成突变结分布来分析,在一边具有高掺杂浓度,而在另一边是低的均匀掺杂浓度,同时假设平板分布忽略结的曲率效应。随后将理想漂移区的电阻与半导体材料的基本特性联系起来<sup>[8]</sup>。

泊松方程的解导出了三角形的电场分布,如图 1.16 所示,在掺杂浓度确定的斜坡场内具有均匀掺杂的漂移区。由漂移区支撑的最大电压由达到半导体材料临界击穿电场 $(E_{\scriptscriptstyle m})$ 的最大电场 $(E_{\scriptscriptstyle m})$ 所决定。然后,由击穿和掺杂浓度对应的临界电场确定最大耗尽宽度 $(W_{\scriptscriptstyle D})$ 。

理想漂移区的特征导通电阻(单位面积电阻)由下式给出

$$R_{\text{on.sp}} = \left(\frac{W_{\text{D}}}{a\mu N_{\text{D}}}\right) \tag{1.8}$$

由于最初将该电阻当做硅器件可达到的最小值,历 史上将其称为漂移区的理想特征导通电阻。最近引 人的电荷耦合概念将在本章后面描述,它可使硅器 件的漂移区电阻减小到比该公式预计值更低。在击 穿情况下,耗尽区宽度由下式给出

$$W_{\rm D} = \frac{2BV}{E_{\rm C}} \tag{1.9}$$

这里 BV 是期望的击穿电压。要想得到该 BV 要求的 漂移区掺杂浓度由下式给出

$$N_{\rm D} = \frac{\varepsilon_{\rm S} E_{\rm C}^2}{2q{\rm BV}} \tag{1.10}$$

图 1.16 理想漂移区及其电场分布

结合这些关系式,可得到理想漂移区的特征电阻

$$R_{\text{on-ideal}} = \frac{4BV^2}{\varepsilon_S \mu_n E_C^3} \tag{1.11}$$

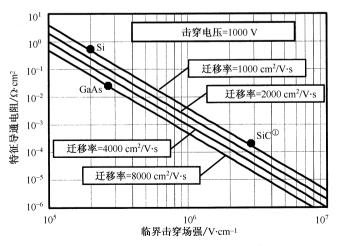

通常将式中的( $\varepsilon_s\mu_n E_c^3$ )命名为功率器件 Baliga 优值(Baliga's figure of merit)。这是半导体材料特性对漂移区电阻影响的标志。漂移区电阻与载流子迁移率的依赖关系,偏好砷化镓和砷化铟这类半导体,这里假设的是电子,因为一般情况下,电子比空穴有更大的迁移率值。然而,对临界击穿电场强度而言,对导通电阻具有更强(三次方)的依赖性,偏好碳化硅这类宽禁带半导体[9]。下一章讨论在半导体中的空穴和电子的碰撞电离系数决定临界击穿电场强度。

作为一个例子,在漂移区特征导通电阻随临界电场强度和迁移率的变化如图 1.17 所示,给出了一个 BV 1000 V 的情况。在图中指出了硅、砷化镓和碳化硅的特性曲线。与硅比较, GaAs 漂移区电阻得到了很大的改善,因为其具有大得多的临界击穿电场强度。与硅比较, SiC 漂移区电阻得到了很大的改善,因为其具有大得多的临界击穿电场强度。以此为基础,在 20 世纪 80 年代开发出优异的 GaAs 高压肖特基整流管<sup>[10]</sup>,在 20 世纪 90 年代开发出优异的 SiC 高压肖特基整流管<sup>[11]</sup>。开发包括氮化镓在内的宽禁带半导体功率器件的兴趣还在继续增长。

图 1.17 理想漂移区特征导通电阻①

① 该图标识, 疑有误——译者注。

## 1.7 电荷耦合结构:理想的特征导通电阻

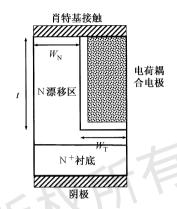

在前一节讨论了在传统结构的阻断模式期间,耗尽区从结或肖特基接触在一维方向延伸。在电荷耦合结构中,通过耗尽层在二维方向的延伸增强电压阻断能力。通过在上表面层水平肖特基接触的形成产生这种效应,如图 1.18 所示,它促进了沿竖直或y方向耗尽区的扩展。同时,通过替换 N 型或 P 型区产生竖直 PN 结,促进沿水平或x方向耗尽区的扩展。这些耗尽区共同在 N 漂移区产生二维电荷耦合,它改变了电场分布。

电荷耦合结构的优化要求选择合适的掺杂浓度及 N 型和 P 型区的厚度。人们已经发现最高的 BV 发生由下式给出的该区域的电荷

$$Q_{\text{optimum}} = 2qN_{\text{D}}W_{\text{N}} = \varepsilon_{\text{S}}E_{\text{C}} \tag{1.12}$$

式中q是电子电荷量 $(1.6\times10^{-19}~\mathrm{C})$ ,  $N_{\mathrm{D}}$ 是 N 型漂移区的掺杂浓度, $W_{\mathrm{N}}$ 是 N 型漂移区的半宽度,如图 1.18 所示, $\varepsilon_{\mathrm{s}}$ 是半导体的介电常数, $E_{\mathrm{C}}$  是半导体中击穿临界电场强度。对于硅,发现基于  $3\times10^{5}~\mathrm{V}\cdot\mathrm{cm}^{-1}$  临界电场强度的优化电荷是 3.11 ×  $10^{-7}~\mathrm{C}\cdot\mathrm{cm}^{-2}$ 。通常用单位面积杂质密度表示这种优化电荷,在这种情况下,对于硅,其值大约是  $2\times10^{12}~\mathrm{cm}^{-2}$ 。可以保证略微低一点的漂移区掺杂浓度,将在下面讨论。

由下式给出电荷耦合结构中漂移区的特征导通电阻

图 1.18 采用 PN 结基极耦合 肖特基二极管结构

$$R_{\text{D,sp}} = \rho_{\text{D}} \left( \frac{p}{W_{\text{N}}} \right) t \tag{1.13}$$

式中 $\rho_{\rm D}$ 是 N 型漂移区的电阻率, t 是沟槽深度, p 是元胞节距。在此, 假设仅沿发生电荷耦合的 沟槽产生均匀电场, 忽略 N 型漂移区剩余部分的电阻。利用电阻率和掺杂浓度之间的关系, 可将该公式写成如下形式

$$R_{\text{D,sp}} = \frac{tp}{q\mu_{\text{N}}N_{\text{D}}W_{\text{N}}} \tag{1.14}$$

将该表达式与式(1.12)结合可得

$$R_{\rm D,sp} = \frac{2tp}{\mu_{\rm N} Q_{\rm optimum}} \tag{1.15}$$

如果沿沟槽电场, 在电荷耦合器件结构中击穿, 假设是均匀的, 其值等于半导体的临界电场强度

$$t = \frac{BV}{E_{\rm C}} \tag{1.16}$$

利用该表达式,以及在式(1.12)中的第二部分,在式(1.15)中得到

$$R_{\text{D,sp}} = \frac{2\text{BV}p}{\mu_{\text{N}}\varepsilon_{\text{S}}E_{\text{C}}^2}$$

(1.17)

这是竖直电荷耦合器件的理想的特征导通电阻的基本表达式。将该表达式与一维情况的比较,参见式(1.11),可以看到电荷耦合器件的特征导通电阻随着 BV 线性增加,而不像传统的漂移区的以更快二次方增长。此外,值得一提的是,可通过减小节距来减小在电荷耦合结构中漂移区的特征导通电阻。发生这种现象是因为当节距减小时漂移区掺杂浓度增加以维持同样的优化电荷。更大的掺杂浓度减小了电阻率和降低了特征导通电阻。然而,电荷耦合器件结构漂移区的特征导通

电阻的分析必须考虑几个方面。首先,必须清楚当掺杂浓度更高时,迁移率变得更低。其次,对于电荷耦合结构,击穿临界电场强度变得更低,因为在漂移区中更高的电场强度扩展更远的距离,产生更强的碰撞电离。如果电荷耦合结构漂移区的击穿临界电场强度降低到  $2 \times 10^5 \text{ V} \cdot \text{cm}^{-1}$ ,对于硅,更合适的是具有相应掺杂密度大约  $1.3 \times 10^{12} \text{ cm}^{-2}$  和优化电荷是  $2.07 \times 10^{-7} \text{ C} \cdot \text{cm}^{-2}$ 。

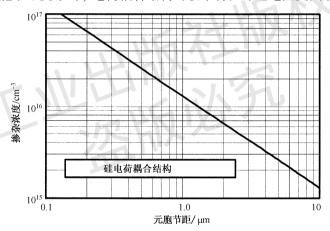

在设计电荷耦合结构漂移区时,不像传统一维情况,重要的是要标示出元胞节距而不是 BV 所对应的漂移区的掺杂浓度。电荷耦合结构的 BV 仅由沟槽深度所决定,沟槽用于提供电荷耦合效应,与 N 型漂移区的掺杂浓度无关。在硅电荷耦合器件中,对于 N 型和 P 型电荷耦合区等宽的情况,图 1.19 所示为 N 型漂移区的掺杂浓度。对于典型的  $1~\mu m$  节距,假设临界电场强度是  $2\times10^5~V\cdot cm^{-1}$ ,N 型漂移区的掺杂浓度大约是  $1.3\times10^{16}~cm^{-3}$ 。

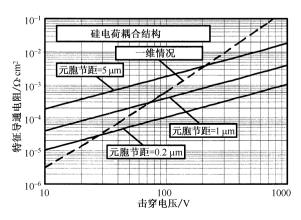

将硅电荷耦合器件中的漂移区的特征导通电阻与一维平板情况相比是非常有趣的。在图 1.20 中,使用电荷耦合结构中的三个元胞节距值进行了这种比较。当元胞节距从 5  $\mu$ m 减小到0.2  $\mu$ m 时,如图 1.19 所示的那样,漂移区的掺杂浓度增加,导致特征导通电阻减小。在图 1.20 中,包含了在特征导通电阻的计算中,随着掺杂浓度增大,迁移率减小的结果。在这两种结构中,特征导通电阻有所交叠。对于 1  $\mu$ m 的元胞节距,交叠大约发生在 70 V 的 BV。当元胞节距增加至 5  $\mu$ m时,交叠移到大约 200 V 的 BV,如果采用小于 0.2  $\mu$ m 的元胞节距,交叠大约发生在 30 V 的 BV。结果是当元胞节距更小时,电荷耦合结构对较小特征导通电阻更具吸引力。

图 1.19 电荷耦合结构漂移区掺杂浓度

图 1.20 电荷耦合结构理想的特征导通电阻(实线:电荷耦合结构;虚线:一维情况)

作为一个特例,考虑设计一个支撑 200 V 的硅器件。在具有一维结的传统结构情况下,如果使用  $3\times10^5$  V·cm<sup>-1</sup>临界击穿电场强度,发现漂移区的特征导通电阻是 3.4 m $\Omega$ ·cm<sup>2</sup>。相反,如果使用  $2\times10^5$  V·cm<sup>-1</sup>临界击穿电场强度,发现具有 1  $\mu$ m 的元胞节距电荷耦合结构漂移区的特征导通电阻仅是 0.86 m $\Omega$ ·cm<sup>2</sup>。在该计算中,对应于漂移区的 N 型部分掺杂浓度为  $1.3\times10^{16}$  cm<sup>-3</sup>,采用 1220 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup>体迁移率。在该例中,电荷耦合结构的漂移区具有 10  $\mu$ m 厚度,而传统结构需要 12.5  $\mu$ m。

图 1.21 所示为产生电荷耦合结构的一个替换方法,从制造的观点看,它更简单。通过使用梯度掺杂分布的结构,在漂移区可以产生一个均匀的电场<sup>[12]</sup>。这些器件已经被验证显著降低肖特基整流管的导通压降,设计出具有低漏电的,阻断电压 30 V~200 V 器件<sup>[13]</sup>。电荷耦合器件的详细讨论已超出本书范围。

#### 1.8 小结

本章论述了功率半导体整流管和晶体管的期望特性。 比较了理想的和典型的硅功率器件特性。在此简要介绍 了各种单极和双极功率器件结构。因为篇幅所限,本书仅 讨论基本的功率器件结构。

图 1.21 采用 MOS 结构的基区 电荷耦合肖特基二极管

#### 习题

- 1.1 定义汽车典型应用的功率器件的电压和电流分类。

- 1.2 定义计算机电源典型应用的功率器件的电压和电流分类。

- 1.3 定义电机控制典型应用的功率器件的电压和电流分类。

- 1.4 定义电力机车典型应用的功率器件的电压和电流分类。

- 1.5 什么是理想功率器件的特性?

- 1.6 描述理想功率整流管的特性。

- 1.7 如何区分理想和实际功率整流管的特性?

- 1.8 描述理想功率晶体管的特性。

- 1.9 如何区分理想和实际功率晶体管的特性?

- 1.10 为什么对于应用单极功率器件结构比双极功率器件更有吸引力?

- 1.11 计算具有  $2000 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$ 电子迁移率和  $5 \times 10^5 \text{ V} \cdot \text{cm}^{-1}$ 临界击穿电场强度半导体的巴利加优值。

- 1.12 确定氮化镓的巴利加优值,假设它具有 900  $\text{cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$ 电子迁移率和 3.3  $\times$  10 $^6$  V  $\cdot$  cm  $^{-1}$  临界击穿电场强度。

## 参考文献

- [1] B. J. Baliga, "Silicon RF Power Devices," World Scientific, Singapore, 2005.

- [2] B. J. Baliga, "Modem Power Devices," Wiley, New York, 1987.

- [3] B. J. Baliga, "Evolution of MOS-Bipolar Power Semiconductor Technology," Proceedings of the IEEE, pp. 409-418, 1988.

- [4] V. A. K. Temple, "MOS Controlled Thyristors (MCTs)," IEEE International Electron Devices Meeting, Abstract 10.7, pp. 282-285, 1984.

- [5] M. Stoisiek and H. Strack, "MOS-GTO-A Turn-off Thyristor with MOS Controlled Emitter Shorts," IEEE International Electron Devices Meeting, Abstract 6.5, pp. 158-161, 1985.

- [6] M. Nandakumar, et al., "A New MOS-Gated Power Thyristor Structure with Turn-off achieved by Controlling the Base Resistance," IEEE Electron Device Letters, Vol. EDL-12, pp. 227-229, 1991.

- [7] B. J. Baliga, "The MOS-Gated Emitter Switched Thyristor," IEEE Electron Device Letters, Vol. EDL-11, pp. 75-77, 1990.

- [8] B. J. Baliga, "Semiconductors for High Voltage Vertical Channel Field Effect Transistors," Journal of Applied Physics, Vol. 53, pp. 1759-1764, 1982.

- [9] B. J. Baliga, "Silicon Carbide Power Devices," World Scientific, Singapore, 2006.

- [10] B. J. Baliga, et al., "Gallium Arsenide Schottky Power Rectifiers," IEEE Transactions on Electron Devices, Vol. ED-32, pp. 1130-1134, 1985.

- [11] M. Bhatnagar, P. M. McLarty, and B. J. Baliga, "Silicon Carbide High Voltage (400V) Schottky Barrier Diodes," IEEE Electron Device Letters, Vol. EDL-13, pp. 501-503, 1992.

- [12] B. J. Baliga, "Schottky Barrier Rectifiers and Method of Forming Same," U. S. Patent 5,612,567, Issued 18 March 1997.

- [13] S. Mahalingam and B. J. Baliga, "The Graded Doped Trench MOS Barrier Schottky Rectifier," Solid State Electronics, Vol. 43, pp. 1-9, 1999.